相位/脉宽鉴相器是利用数字部件构成的鉴相电路,这种电路既简单又便于使用,它可把输入端信号间的相位差转换成脉冲宽度。该脉宽既可利用低通滤波器将其变成模拟输出电压,构成模拟鉴相电路,也可直接通过数字电路将其变成数字量,组成相位/数字鉴相电路。相位/脉宽鉴相器要求输入信号和参考信号必须都是方波序列脉冲信号,若不是方波信号,则应首先采用过零检测电路或放大整形电路将它们变成方波信号。电路根据输入和参考信号过零点的时间来工作,其输出亦为脉冲信号,脉冲宽度与两个输入波形之间的过零时间差(相位差)成比例,而与波形的其他部分无关。相位/脉宽鉴相电路通常用门电路和触发器组成。

1.异或门鉴相器

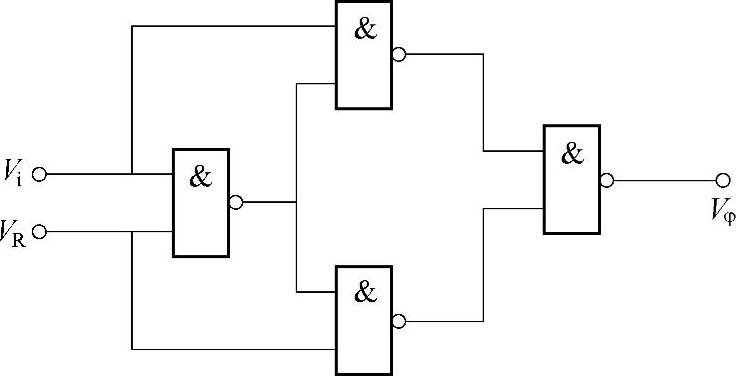

异或门电路是指,当有两个输入信号时,在一个为1、另一个为0的情况下,输出为1,否则输出为0的电路,或者说,“异”者为1,“同”者为0。能完成这种功能的异或门集成电路有74LS86和CD4070B等,也可由4个与非门电路组成,如图3-30所示。

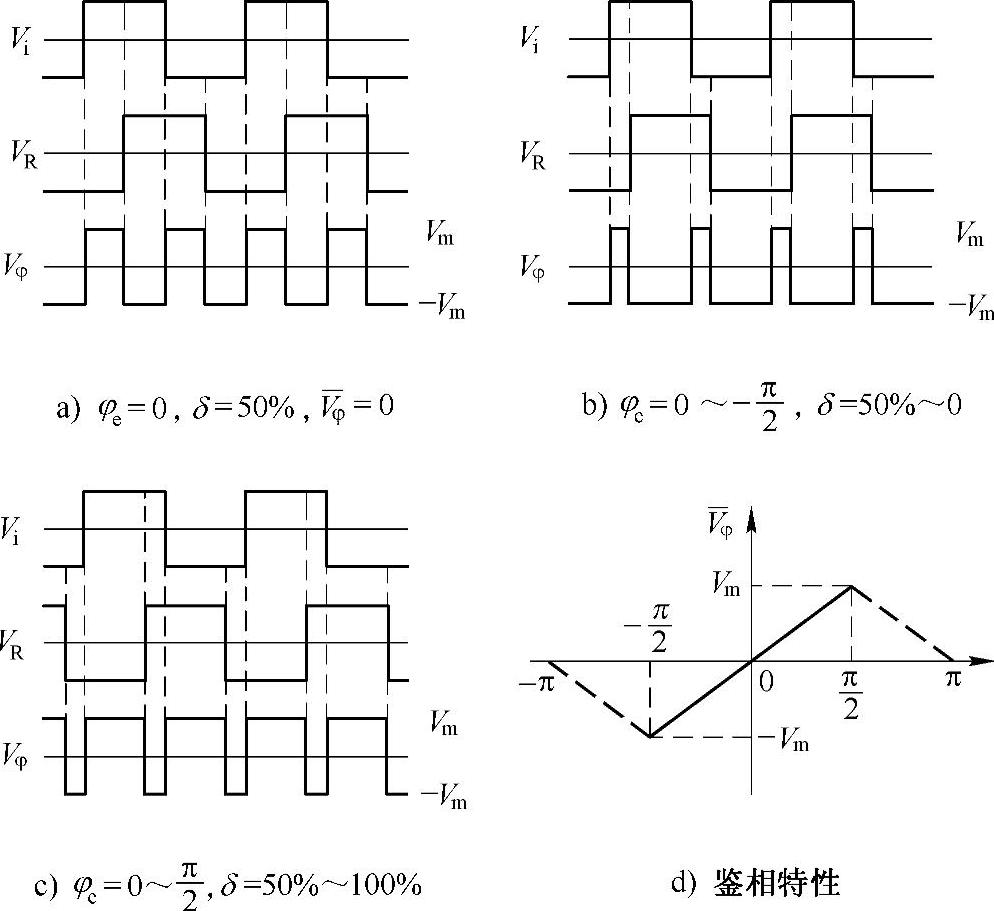

设VR、Vi为两个同周期的对称方波信号。当瞬时相位差φe=0时,这两个信号之间具有π/2的初始固有相位移。这时异或门的输出电压Vφ为对称方波(占空比δ=50%),频率为输入信号的2倍。其波形如图3-31a所示,输出电压的平均值 。

。

图3-30 异或门鉴相器

当瞬时相位差 时,相当于在图3-31a的基础上,把Vi的波形向右移,使Vi与VR波形的上升沿接近,异或门输出信号的占空比δ=50%~0,其平均值Vφ必为负,如图3-31b所示。当两个波形的上升沿对齐时,即Vi与VR同相,瞬时相位差

时,相当于在图3-31a的基础上,把Vi的波形向右移,使Vi与VR波形的上升沿接近,异或门输出信号的占空比δ=50%~0,其平均值Vφ必为负,如图3-31b所示。当两个波形的上升沿对齐时,即Vi与VR同相,瞬时相位差 ,δ=0,输出电压的平均值达到最大,

,δ=0,输出电压的平均值达到最大, 。

。

当瞬时相位差 时,相当于在图3-31a的基础上,把Vi的波形向左移,使Vi的上升沿与VR波形的下降沿相接近,输出信号的占空比δ=50%~100%,其平均值Vφ为正值,如图3-31c所示。当Vi的上升沿与VR的下降沿对齐时,瞬时相位差

时,相当于在图3-31a的基础上,把Vi的波形向左移,使Vi的上升沿与VR波形的下降沿相接近,输出信号的占空比δ=50%~100%,其平均值Vφ为正值,如图3-31c所示。当Vi的上升沿与VR的下降沿对齐时,瞬时相位差 ,占空比δ=100%,输出电压的平均值达到正的最大,即

,占空比δ=100%,输出电压的平均值达到正的最大,即 。

。

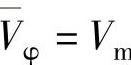

综上所述,异或门鉴相器的鉴相特性为三角形特性,如图3-31d所示。输出电压的平均值及线性范围分别为

图3-31 异或门鉴相器的波形及鉴相特性

式中,Vm为输出脉冲的幅值。

式(3-41)和式(3-42)表明,异或门鉴相器的线性范围较小,且要求两个输入信号的占空比δ必须为50%,即它们是等宽方波。

2.R-S触发器鉴相器

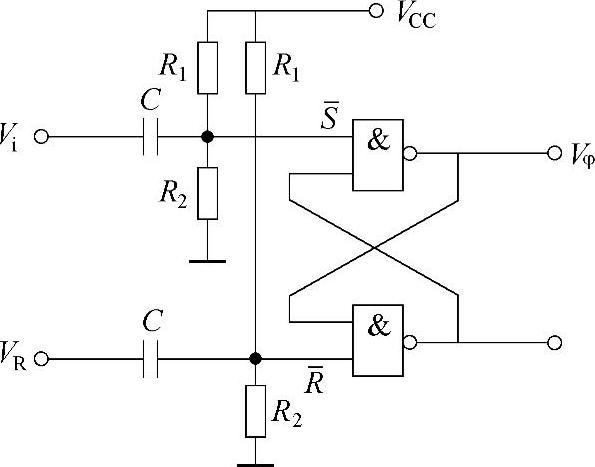

由触发器组成的鉴相器可由R-S触发器实现,也可由J-K触发器实现。图3-32为由与非门组成的R-S触发器鉴相器。

在图3-32中,由电阻R1、R2构成分压电路,使触发器的 、

、 端均为高电平,R1、R2又与电容C组成微分电路,由信号波形的下降沿产生负脉冲使电路翻转。

端均为高电平,R1、R2又与电容C组成微分电路,由信号波形的下降沿产生负脉冲使电路翻转。

图3-32 R-S触发器鉴相器(www.zuozong.com)

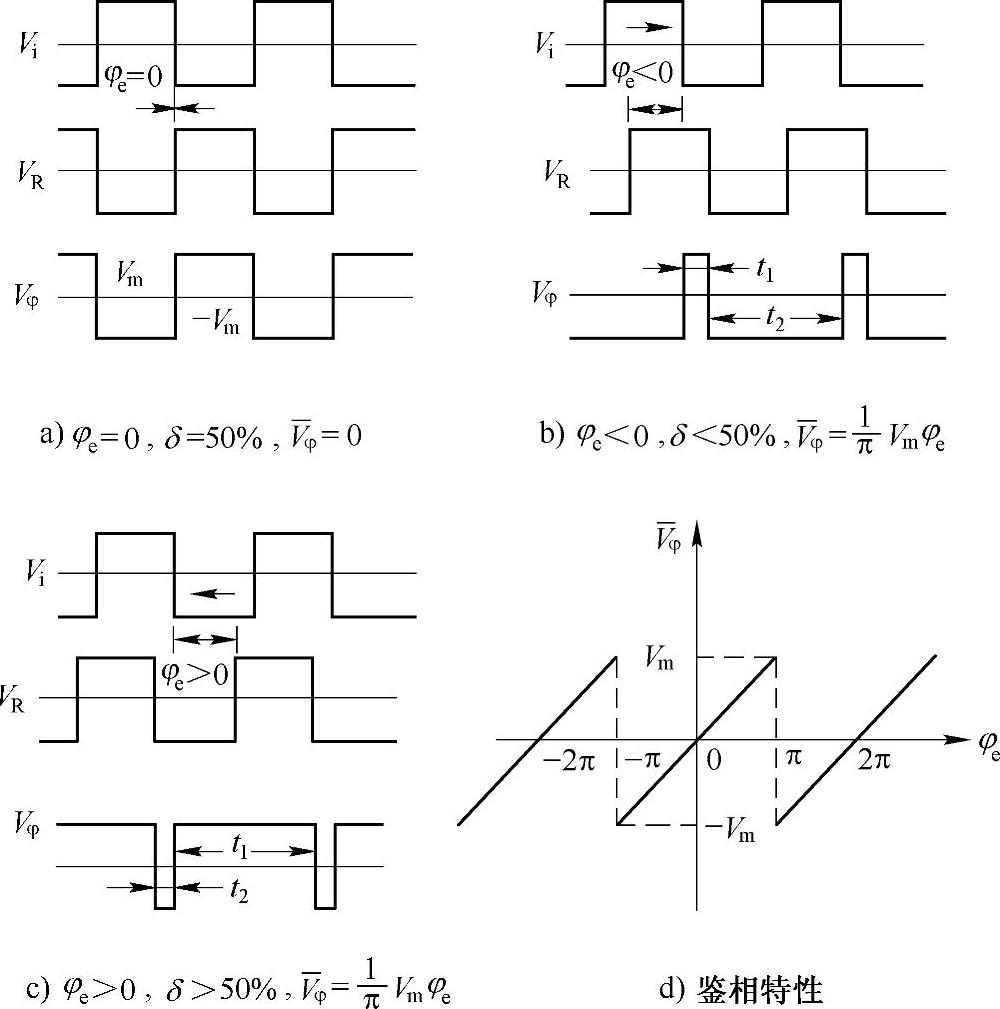

根据R-S触发器的逻辑特性,可分别画出φe=0、φe<0和φe>0的输出信号的波形及鉴相特性,如图3-33所示。

图3-33 R-S触发器鉴相器的波形及鉴相特性

由图3-33可见,R-S触发器的鉴相特性为锯齿特性。输出电压的平均值及线性范围分别为

显然,R-S触发器鉴相器的线性范围比异或门鉴相器扩大了1倍,而且由于采用输入信号和参考信号的下降沿触发电路,故对输入信号和参考信号波形的占空比无特殊要求。但是,在这种方案中利用RC微分网络提取跳变触发信号,虽然简单,却易受干扰而产生误触发。

3.J-K触发器鉴相器

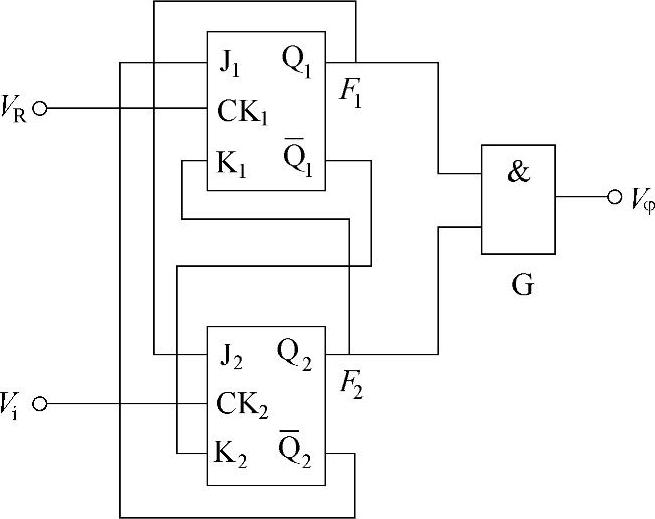

用两个J-K触发器组成的边沿触发型鉴相器如图3-34所示。

图3-34 J-K触发器鉴相器

该电路的特点是:由于F1的输出Q1和 分别接F2的J2和K2,所以F2在CK2端受下降沿触发后,建立的状态与F1相同;F2的输出Q2和

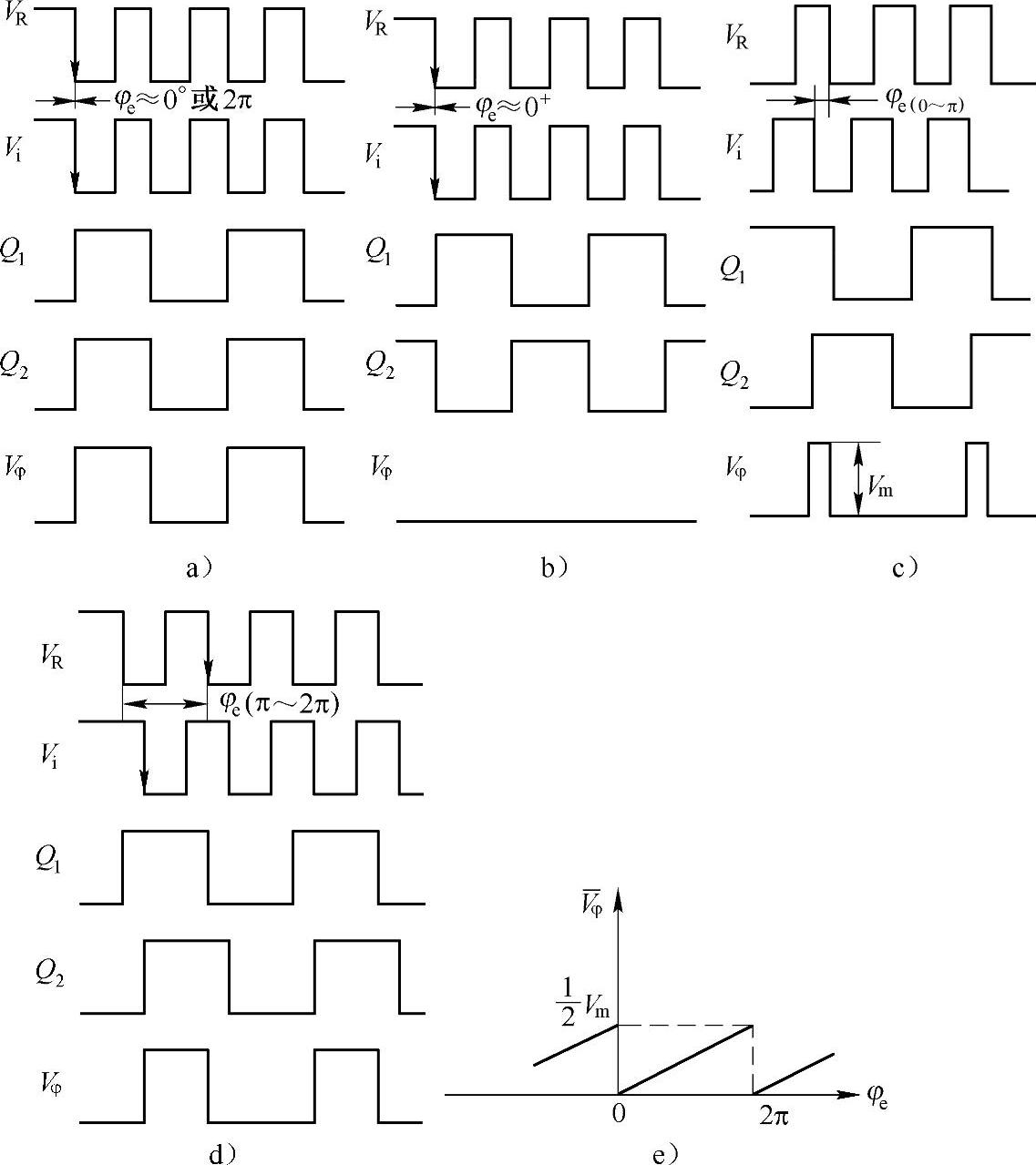

分别接F2的J2和K2,所以F2在CK2端受下降沿触发后,建立的状态与F1相同;F2的输出Q2和 分别作为F1的K1和J1的输入,所以F1在CK1端受下降沿触发后,建立的状态与F2相反。根据上述特点,并考虑到F1和F2是下降沿触发的J-K触发器,就可分别画出当φe=0、φe<0及φe>0时Q1和Q2的输出波形以及经过与门后的输出脉冲波形和鉴相特性,如图3-35所示。

分别作为F1的K1和J1的输入,所以F1在CK1端受下降沿触发后,建立的状态与F2相反。根据上述特点,并考虑到F1和F2是下降沿触发的J-K触发器,就可分别画出当φe=0、φe<0及φe>0时Q1和Q2的输出波形以及经过与门后的输出脉冲波形和鉴相特性,如图3-35所示。

图3-35 J-K触发器鉴相器的波形及鉴相特性

由图3-35可见,J-K触发器鉴相器的鉴相特性亦为锯齿特性,输出电压平均值及鉴相线性范围分别为

0<φe<2π (3-46)

φe=0,2π,4π,…点是奇异点,其 值不确定。所以J-K触发器鉴相器的有效鉴相范围为2π。它在整个相位差范围内都是线性的。由于取消了R-S触发器中的RC微分网络,所以提高了电路的抗干扰能力。

值不确定。所以J-K触发器鉴相器的有效鉴相范围为2π。它在整个相位差范围内都是线性的。由于取消了R-S触发器中的RC微分网络,所以提高了电路的抗干扰能力。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。